#### 香港中文大學

The Chinese University of Hong Kong

CENG3430 Rapid Prototyping of Digital Systems

# Lecture 12: VHDL versus Verilog

#### **Outline**

- VHDL vs. Verilog

- Background

- Syntax and Popularity

- Operators

- Overall Structure

- External I/O Declaration

- Concurrent Statements

- Sequential Statements

- Edge Detection

- Wire vs. Reg

- Structural Design

- Design Constructions

- Case Study: Flip-flop

### What are VHDL and Verilog?

- They are both hardware description languages for modeling hardware.

- They are each a notation to describe the behavioral and structural aspects of an electronic digital circuit.

### **VHDL: Background**

- VHSIC Hardware Description Language

- VHSIC: Very High Speed Integrated Circuit.

- Developed by Department of Defense (1981)

- In 1986 rights where given to IEEE.

- Became a standard and published in 1987.

- Revised standard we know now published in 1993 (VHDL 1076-1993) regulated by VHDL international (VI).

### **VHDL: Design Concept**

- VHDL uses top-down approach to partition a design into small building blocks (i.e., components).

- Entity: Describe interface signals and basic building blocks.

- Architecture: Describe behavior, each entity can have multiple Architectures.

Connected by port map in architecture body

# Verilog: Background

- Developed by Gateway Design Automation (1980)

- Later acquired by Cadence Design (1989) who made it public in 1990

- Became a standardized in 1995 by IEEE (Std 1364)

regulated by Open Verilog International (OVI)

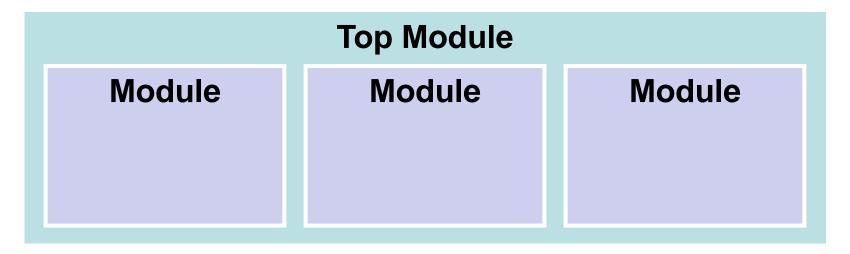

### **Verilog: Design Concept**

- The building block in Verilog is called module.

- There is only one module per file (.v) usually.

- Modules connect through their ports (similarly as in VHDL).

- A top level module invokes instances of other modules.

Connected by relating I/O and internal wires

# Syntax and Popularity

#### **Popularity**

**VHDL** is more popular with European companies.

**Verilog** is more popular with US companies.

#### **Programming Style (Syntax)**

VHDL is similar to Ada programming language. **Verilog** is similar to C/Pascal programming language.

VHDL is NOT case-sensitive. Verilog is case-sensitive.

VHDL is more "verbose" than Verilog.

# **Operators**

|                | VHDL | Verilog |                    | VHDL  | Verilog |

|----------------|------|---------|--------------------|-------|---------|

| Add            | +    | +       | Bitwise Negation   | not   | ~       |

| Subtract       | _    | -       | Bitwise NAND       | nand  | ~ &     |

| Multiplication | *    | *       | Bitwise NOR        | nor   | ~       |

| Division       | /    | /       | Bitwise XNOR       | xnor  | ~^      |

| Modulo         | mod  | %       | Greater (or Equal) | >, >= | >, >=   |

| Absolute       | abs  | N/A     | Less (or Equal)    | <, <= | <, <=   |

| Exponentiation | **   | **      | Logical Equality   | =     | ==      |

| Concatenation  | &    | { , }   | Logical Inequality | /=    | !=      |

| Left Shift     | sll  | <<      | Logical AND        | and   | & &     |

| Right Shift    | srl  | >>      | Logical OR         | or    | 11      |

| Bitwise AND    | and  | &       | Logical Negation   | not   | !       |

| Bitwise OR     | or   | 1       | Case Equality      | N/A   | ===     |

| Bitwise XOR    | xor  | ^       | Case Inequality    | N/A   | !==     |

#### **Outline**

#### VHDL vs. Verilog

- Background

- Syntax and Popularity

- Operators

- Overall Structure

- External I/O Declaration

- Concurrent Statements

- Sequential Statements

- Edge Detection

- Wire vs. Reg

- Structural Design

- Design Constructions

- Case Study: Flip-flop

#### **Overall Structure**

CENG3430 Lec12: VHDL versus Verilog

```

VHDL (.vhd)

Verilog (.v)

-- Library Declaration

// One Module

module mux ( ... );

library IEEE;

-- Entity Declaration

entity mux is

end mux

-- Architecture Body

architecture arch of mux is

begin

endmodule

end arch;

```

#### **External I/O Declaration**

#### **VHDL**

-- Library Declaration

•••

-- Entity Declaration

entity mux is

```

port(a,b,s: in std_logic;

y: out std_logic);

```

end mux

-- Architecture Body

architecture arch of mux is

begin

. . .

end arch;

```

Verilog

```

// One Module

```

module mux (a, b, s, y);

input a,b,s;

output y;

```

### **Concurrent & Sequential Statements**

#### **VHDL**

#### Verilog

#### -- Entity Declaration

```

entity mux is

```

```

y: out std logic);

```

end mux

architecture arch of mux is -- concurrent statements

begin

#### -- concurrent statements

#### process (...) begin

-- sequential statements end process;

end arch;

// One Module

module mux (a, b, s, y);

output y;

always @(...)

begin

-- sequential statements end process;

endmodule

#### 1) Concurrent Statement

**VHDL:** inside architecture body, outside the process

```

signal a, b: std_logic vector(7 downto 0); -- array

signal c, d, e: std logic;

a(3 \text{ downto } 0) \leq b(7 \text{ downto } 4);

b(7 \text{ downto } 4) \le "0000";

c <= d and e; -- bitwise AND

```

#### LHS <= RHS;

- LHS must be signal.

- The LHS will be updated whenever RHS changes.

```

Verilog: outside the always@block

```

```

wire [7:0] a, b; // array

wire c, d, e;

assign a[3:0] = c[7:4];

assign b[7:4] = 'b0000; // binary

assign c = d & e; // bitwise AND

```

#### assign LHS = RHS;

- LHS must be wire.

- The LHS will be updated whenever RHS changes.

#### **Class Exercise 12.1**

Student ID: \_\_\_\_\_ Date: Name: \_\_\_\_

Translate the following VHDL program to Verilog:

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity abc is

port (a,b,c: in std logic;

y: out std logic);

end abc;

architecture abc arch of

abc is

signal x : std logic;

begin

x \le a \text{ nor } b;

y \le x and c;

end abc arch;

```

# 2) Sequential Statement

```

VHDL

Verilog

architecture arch of ex is module ex (...);

begin

reg a, b, c;

( conditions )

process ( sensitivity list )

always @

variable a, b, c;

begin

begin

// LHS must be reg (not wire)

-- LHS could be signals

(suggested) or variables

-- signal assignment (<=)

// blocking assignment (=)

for both combinational logic

for combinational logic

// non-blocking assignment

and sequential logic

-- variable assignment (:=)

(<=) for sequential logic

end;

end

```

endmodule

end arch;

# 2) Sequential Statements: Blocking

- Blocking assignments (=) in a sequential block (i.e., always@) are executed before the execution of the statements that follow it.

- All blocking assignments are executed in a sequentially way.

- Usage: Use blocking assignments in always@ blocks to synthesize combinational logic (i.e. no clock!).

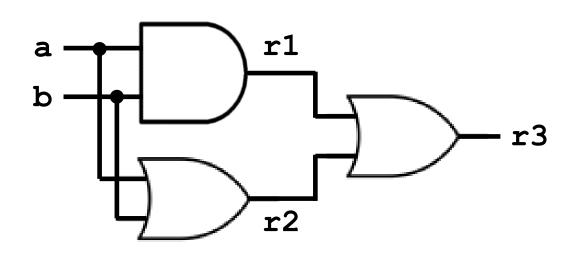

### **Class Exercise 12.2**

Student ID: \_\_\_\_\_ Date: Name: \_\_\_\_

Translate the following Verilog program to VHDL:

```

reg r1, r2, r3;

always @ (a or b)

begin

r1 = a \& b;

r2 = a | b;

r3 = r1 | r2;

end

```

# 2) Sequential Statements: Non-Blocking

- Non-blocking assignments (<=) in a sequential block (i.e., always@) are executed within the same time step regardless of the order.

- All non-blocking assignments will take effect at the next clock edge (concurrently, not sequentially!).

- Usage: Use non-blocking assignments in always@ blocks to synthesize sequential logic (i.e. has clock!).

```

reg r1, r2;

...

always @ (posedge clk)

begin

→ r1 <= a;

→ r2 <= r1;

end

```

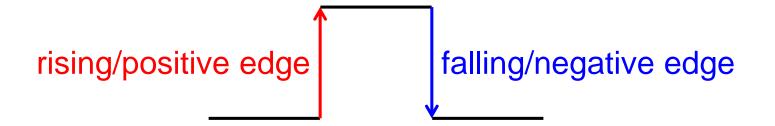

### **Edge Detection**

#### **VHDL**

```

process (clk)

begin

sensitivity list

if rising_edge (CLK)

or

if falling_edge (CLK)

conditions

```

#### Verilog

```

always @ (posedge clk)

or

always @ (negedge clk)

begin

conditions

```

end

end

### **Class Exercise 12.3**

Student ID: \_\_\_\_\_ Date: Name: \_\_\_\_

Translate the following Verilog program to VHDL:

```

reg r1, r2;

...

always @ (posedge clk)

begin

r1 <= a;

r2 <= r1;

end</pre>

```

# "wire" vs. "reg" in Verilog

- Wire: Has <u>no</u> memory

- It must be physical wire in the circuit.

- It does not hold the value.

- Usage: Cannot use "wire" in the left-hand-side of assignments inside always@ blocks!

- Reg: Has memory

- It could be a flip-flop or a physical wire.

- It holds the value until a new value is assigned.

- Usage: Cannot use "reg" in the left-hand side of assignments <u>outside</u> always@ blocks (i.e., concurrent assignment)!

#### **Outline**

#### VHDL vs. Verilog

- Background

- Syntax and Popularity

- Operators

- Overall Structure

- External I/O Declaration

- Concurrent Statements

- Sequential Statements

- Edge Detection

- Wire vs. Reg

- Structural Design

- Design Constructions

- Case Study: Flip-flop

# Structural Design in VHDL (1/2)

Structural Design in VHDL: Like a circuit but describe

it by text.

Component A

Component B

Component C

Connected by port map in architecture body

- **Design Steps:**

- Step 1: Create entities

- Step 2: Create components from entities

- Step 3: Use "port map" to relate the components

### Structural Design in VHDL (2/2)

```

1 library IEEE;

1 library IEEE;

2 use IEEE.STD LOGIC 1164.ALL;

2 use IEEE.STD LOGIC 1164.ALL;

3 entity and2 is

Step 1

4 port (a,b: in STD LOGIC;

4 entity test is

c: out STD LOGIC );

5 port (in1: in STD LOGIC; in2: in STD LOGIC;

6 end and2;

6 in3: in STD LOGIC;

7 architecture and2 arch of and2 is

7 out1: out STD LOGIC );

8 begin

8 end test;

c \le a and b;

9 architecture test arch of test is

10 end and2 arch;

10 component and2 --create component

Step 2

11

port (a,b: in std logic; c: out std logic);

12 library IEEE;

12 end component;

13 use IEEE.STD LOGIC 1164.ALL;

13 component or 2 -- create component

14 entity or2 is

port (a,b: in std logic; c: out std logic);

Step 1

15 port (a,b: in STD LOGIC;

15 end component;

c: out STD LOGIC);

16 signal inter sig: std logic;

Step 3

17 end or2;

17 begin

18 architecture or 2 arch of or 2 is

18 label1: and2 port map (in1, in2, inter sig);

19 begin

19 label2: or2 port map (inter sig, in3, out1);

20 end test arch;

20 c <= a or b;

inter sig

in1 -

21 end or2 arch;

CENG3430 Lec12: VHDL versus Verilog

29

```

# Structural Design in Verilog (1/2)

Structural Design in Verilog: One top module, several (sub) modules.

Connected by relating I/O and internal wires

Design Steps:

Step 1: Create (sub) module(s) (usually in separate .v files)

Step 2: Define a top-module to interconnect module (s)

### Structural Design in Verilog (2/2)

#### and2.v

```

module and2( Step 1

input a,

input b,

output c

);

assign c = a & b;

endmodule

```

#### or2.v

```

module or2(

input a,

input b,

output c

);

assign c = a | b;

endmodule

```

#### top\_module.v

```

Step 2

module top module (

input in1, input in2, input in3,

output out1);

wire inter sig;

and2 ins(

.a(in1),

.b(in2),

.c(inter sig)

or2 or2 ins(

.a(inter sig),

.b(in3),

.c (out1)

inter sig

in1

out1

in3

endmodule

```

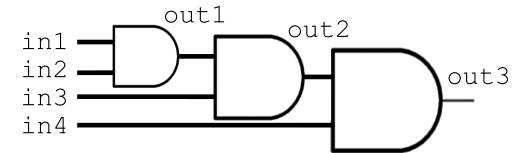

#### **Class Exercise 12.4**

Student ID: \_\_\_\_\_ Date: Name: \_\_\_\_

Implement the following circuit in Veirlog:

### **Design Constructions (1/4)**

```

in1 ____ out1

```

VHDL: when-else (concurrent, outside process)

```

architecture arch of ex is

begin

out1 <= '1' when in1 = '1' and in2 = '1' else '0';

end arch ex_arch;</pre>

```

**Verilog:** assign ? : (concurrent, outside always@ block)

```

module ex (...);

assign out1 = (in1=='b1 && in2=='b1) ? 'b1 : 'b0;

// 'b: binary; 'o: octal; 'd: decimal; 'h: hexadecimal

endmodule

```

### **Design Constructions (2/4)**

```

VHDL: if-then-else

(sequential, inside process)

process (in1, in2)

begin

if in1='1' and in2='1'

then

out1 <= '1';

else

out1 <= '0';

end if;

end process;

```

```

Verilog: if-else

(sequential, inside always@)

always @(in1, in2)

begin

if (in1=='b1 && in2=='b1)

begin

out1 = 'b1;

end

else

begin

out1 = 'b0;

end

end

```

# **Design Constructions (3/4)**

```

VHDL: case-when

process (b)

begin

case b is

when "00" | "11" =>

out1 <= '0';

out2 <= '1';

when others =>

out1 <= '1';

out2 <= '0';

end case;

end process;

CENG3430 Lec12: VHDL versus Verilog

```

```

Verilog: case

(sequential, inside process) (sequential, inside always@)

always @(b)

begin

case (b)

'b00 || 'b11:

out1 = 'b0;

out2 = 'b1;

default:

out1 = 'b1;

out2 = 'b0;

endcase

end

```

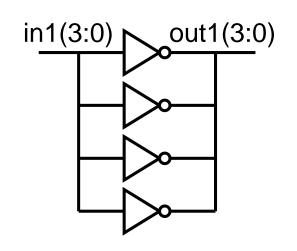

### **Design Constructions (4/4)**

```

VHDL: for-in-to-loop

(sequential, inside process)

process(in1)

begin

for i in 0 to 3 loop

out1(i) <= not in1(i);

end loop;

end process;</pre>

```

```

Verilog: for-loop

(sequential, inside always@)

always @(in1)

begin

for(idx=0; idx<4; idx+=1)

begin

out1[idx] = ~in1[idx];

end

end</pre>

```

#### **Outline**

#### VHDL vs. Verilog

- Background

- Syntax and Popularity

- Operators

- Overall Structure

- External I/O Declaration

- Concurrent Statements

- Sequential Statements

- Edge Detection

- Wire vs. Reg

- Structural Design

- Design Constructions

- Case Study: Flip-flop

### Posedge Flip-flop with Sync Reset (1/2)

```

VHDL

Verilog

module dff(

entity dff is

port (D, CLK, RESET:

input D,

in std logic;

input CLK,

Q: out std logic);

input RESET,

end dff;

output reg Q);

always @ (posedge CLK)

architecture dff arch of

dff is begin

begin

process (CLK) begin

if rising edge (CLK) then if (RESET) begin

if (RESET = '1') then

Q <= 1'b0;

O <= 'O';

end

else

else begin

Q \leftarrow D;

Q <= D;

end if;

end

end if;

end process;

end

end dff arch;

endmodule

```

# Posedge Flip-flop with Sync Reset (2/2)

```

Verilog

module dff(

input D,

input CLK,

input RESET,

output reg Q);

always @ (posedge CLK)

begin

```

```

■ Input must be wire.

```

- Output could be either wire or reg.

- The default option is wire.

- But you can specify an output as wire or reg depending on how you will assign it a value.

```

if (RESET) begin

Q <= 1'b0;

end

else begin

Q <= D;

end</pre>

```

end endmodule

### Posedge Flip-flop with Async Reset (1/2)

#### **VHDL** Verilog module dff( entity dff is port (D, CLK, RESET: input D, in std logic; input CLK, Q: out std logic); input RESET, end dff; output reg Q); architecture dff arch of always @ (posedge CLK or dff is begin posedge RESET) process (CLK, RESET) begin begin if (**RESET = '1'**) if (**RESET**) begin Q <= 1'b0; then O <= 'O'; end elsif rising edge (CLK) else begin then Q <= D; $Q \ll D;$ end end if; end process; end end dff arch; endmodule

# Posedge Flip-flop with Async Reset (2/2)

```

Verilog

module dff(

input D,

input CLK,

input RESET,

output reg Q);

always @ (posedge CLK or

posedge RESET)

```

```

Question: What if we do not specify "posedge" for the RESET signal?

```

begin

if (RESET) begin

Q <= 1'b0;

end

else begin

Q <= D;</pre>

end

endmodule

end

[Synth 8-434] mixed <u>level sensitive</u> and <u>edge triggered</u> event controls are **not supported** for synthesis!

positive level

positive edge

negative edge

negative level

negative level

### **Summary**

- VHDL vs. Verilog

- Background

- Syntax and Popularity

- Operators

- Overall Structure

- External I/O Declaration

- Concurrent Statements

- Sequential Statements

- Edge Detection

- Wire vs. Reg

- Structural Design

- Design Constructions

- Case Study: Flip-flop